## Embedded Thermal Energy Harvesting Challenges & Opportunities

**M. Keller**, J. Goeppert, Y. Manoli, G. Savelli, J.-P. Colonna, P. Faucherand, L.-M., Collin, L. Fréchette

Smart Technologies for eneRgy Efficient Active cooling in Advanced Microelectronic Systems

- Implementation of a **self-adaptive** microfluidic cooling system

- Minimization of the **pumping power** dedicated to coolant

- Enhancement of the surface temperature uniformity of the interposer

#### µTEG – Design & Implementation

- Integrated Digital Circuit Design

@ Ultra-low Supply Voltages

- Conclusion

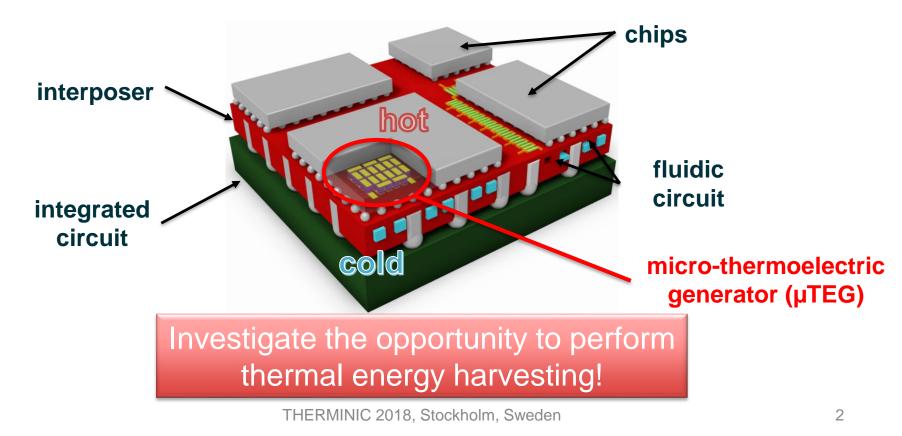

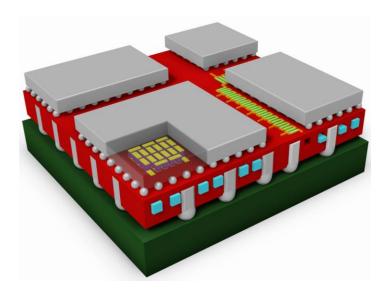

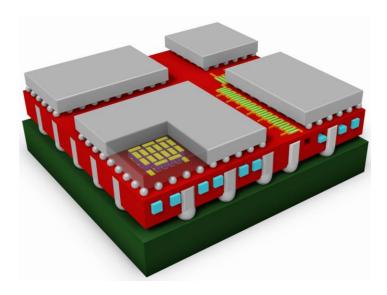

- 1. Design & implement a 2.5D  $\mu$ TEG which

- harvests power of several mWs

- consists of materials that can be processed using standard fabrication steps of integrated circuits

- 2. Integrate four  $\mu$ TEGs into a demonstrator which consists of

- four ASICs (hot source) cooled by means of

- fluidic microchannels (cold source)

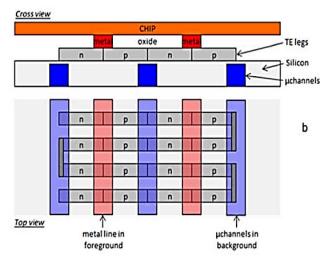

2D architecture (planar)

top view

- lines consisting of either n- or p-type materials

- in-plane thermal & electrical flow

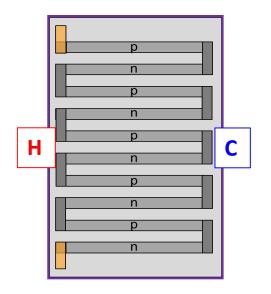

3D architecture (cross-plane)

cross-sectional view

- legs consisting of either n- or p-type materials

- out-of-plane thermal & electrical flow

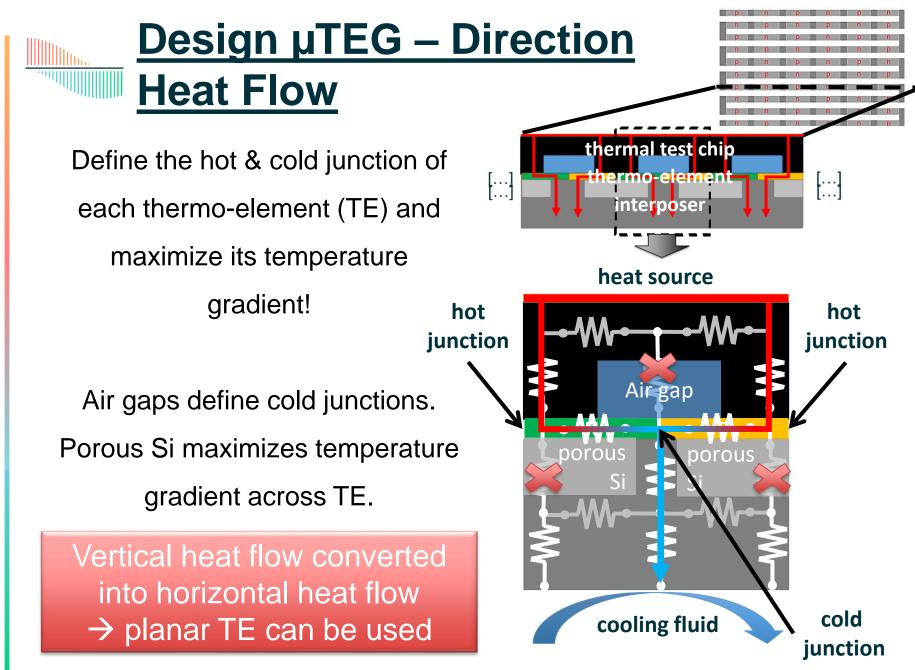

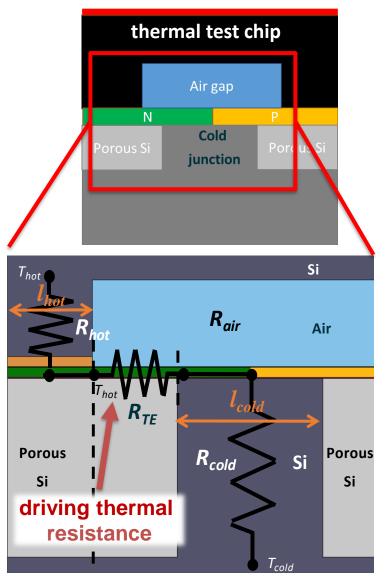

## 2.5D architecture (combined)

cross-sectional & top view

- lines consisting of n- & ptype segments

- thermal flow: out-of-plane

- electrical flow: in-plane

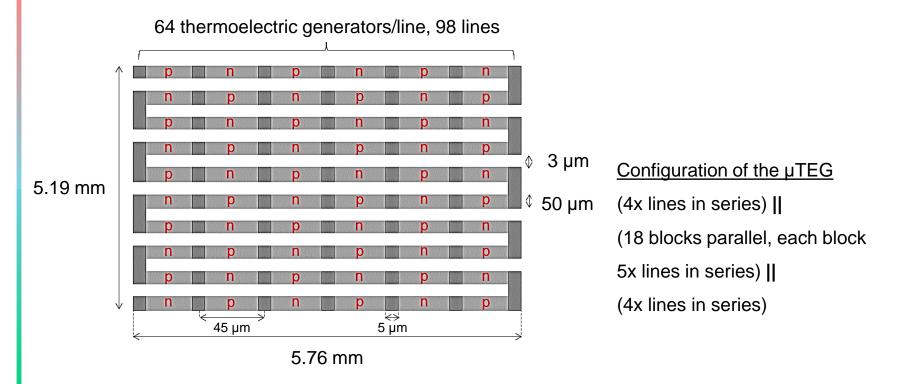

#### Design objective: Harvest > 1mW

$\rightarrow$  Maximize number of thermo-elements on the given area

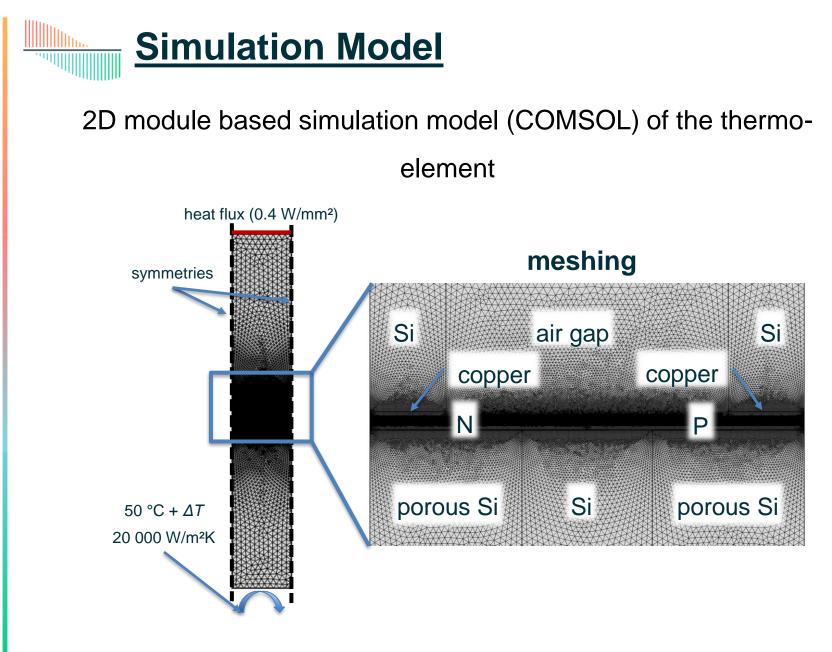

Design & simulation: in-house software & COMSOL

Design objective: Use materials that can be processed using standard fabrication steps of integrated circuits!

$\rightarrow$  polycrystalline SiGe and quantum dots super lattices (QDSL)

|      |        | electrical<br>resistivity<br>ρ (Ωμm) | Seebeck<br>coefficient<br>S (µV/K) |

|------|--------|--------------------------------------|------------------------------------|

| SiGe | n-type | 34                                   | -185                               |

|      | p-type | 30                                   | +142                               |

| QDSL | n-type | 95                                   | -268                               |

|      | p-type | 160                                  | +253                               |

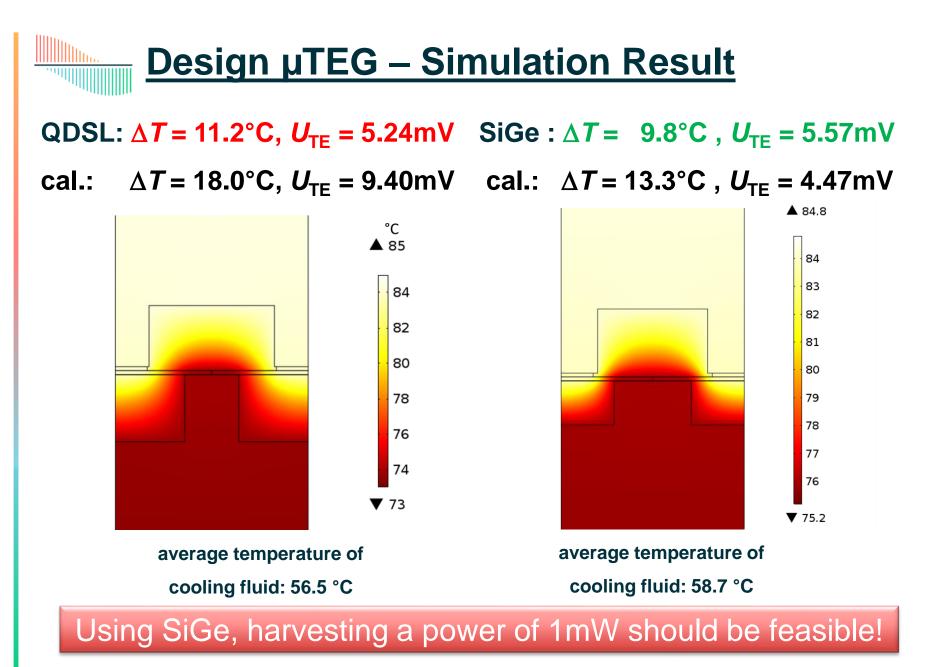

$$Dbjective: Harvest > 1mW/\muTEG$$

$$P = 1mW = \frac{1}{R_{\mu TEG}} \left(\frac{V_{OC}}{2}\right)^2 \approx \frac{1}{\frac{320}{18}\rho_{TE}} \left(\frac{320 * V_{TE}}{2}\right)^2$$

#### minimum voltage V<sub>TE</sub> per thermo-element

$$1 \text{mW} = \frac{1}{\frac{1}{18} \frac{(30+34)\Omega\mu\text{m}}{2} \frac{100\mu\text{m}}{2\mu\text{m} * 50\mu\text{m}}} \frac{320}{4} V_{TE}^2 \rightarrow V_{TE} \approx 4.71 \text{ mV}$$

#### required minimum temperature drop $\Delta T$

$$V_{TE} = S * \Delta T \rightarrow \Delta T \approx \mathbf{13.3}^{\circ}C$$

#### <u>Notes</u>

- parameters given on previous slides

- results for QDSL: 9.4mV / 18°C

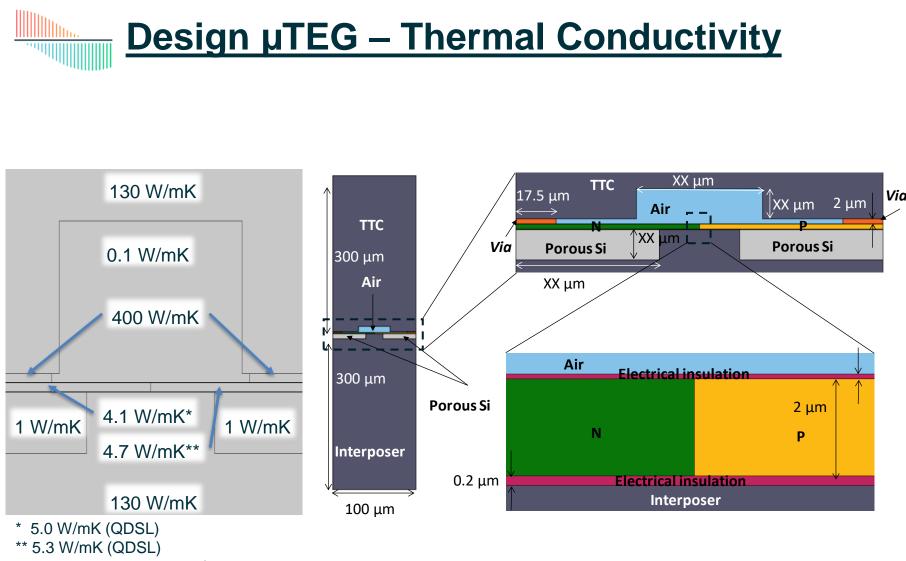

## Design µTEG – Energy Harvesting vs.

Cooling Efficiency

trade-off: harvested energy  $(R_{\text{TE,th}} \uparrow)$  $\leftrightarrow$  cooling efficiency  $(R_{\text{TE,th}} \downarrow)$

$T_{\rm chip,max} = 85^{\circ}{\rm C}$

→ Adapt the thermal resistance R<sub>TE,th</sub> of the thermo-element by adapting the lengths of the air gap and the porous silicon.

Thermal resistance of the thermo-elements can be adapted easily!

electrical insulation: 1.4 W/mK

- µTEG Design & Implementation

- Integrated Digital Circuit Design

@ Ultra-low Supply Voltages

- Conclusion

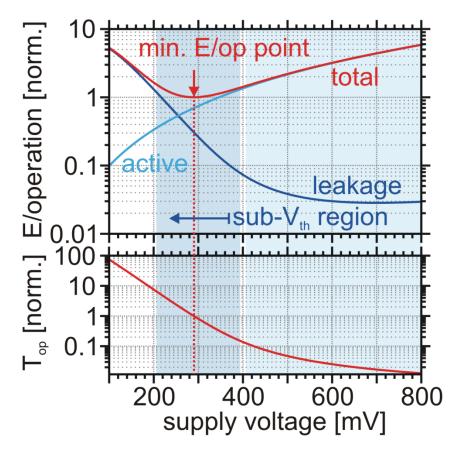

## <u>Supply Voltage Scaling –</u> <u>Minimum Energy/Operation</u>

- Iow voltage / Iow power above threshold

→ 500mV < V<sub>DD</sub> < 1000mV</li>

- minimum energy/operation near-threshold

→ 200mV < V<sub>DD</sub> < 400mV</li>

Example: 130nm technology,  $V_{\rm T} \approx 250 {\rm mV}$

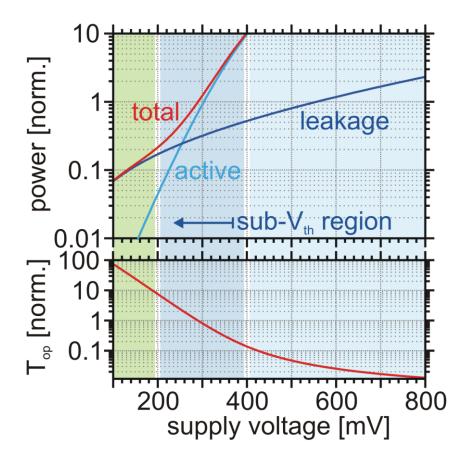

## Supply Voltage Scaling – Minimum Energy/Operation

- low voltage / low power

above threshold

→ 500mV < V<sub>DD</sub> < 1000mV</li>

- minimum energy/operation near-threshold

→ 200mV < V<sub>DD</sub> < 400mV</li>

- minimum power

sub-threshold

→ V<sub>DD</sub> as low as possible

Example: 130nm technology,  $V_{\rm T} \approx 250 {\rm mV}$

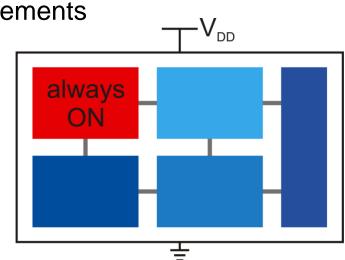

# Why supply voltage reduction below minimum energy per operation point?

- always-on circuits with low speed requirements

- wake-up circuits

- state-holding elements

- $\rightarrow$  reduction of stand-by power

- only low supply voltages available

- energy harvesting

- $\rightarrow$  thermoelectric generators or fuel cells

## <u>Supply Voltage Reduction –</u> Limiting Factors

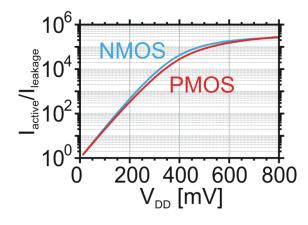

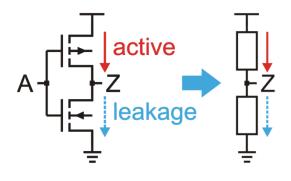

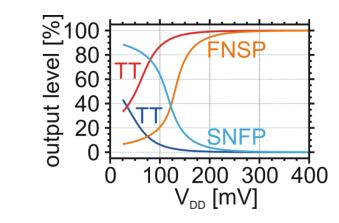

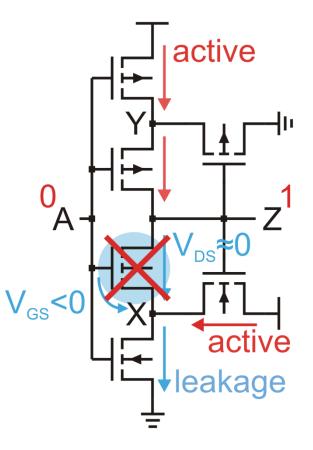

- on- to off-current ratio decreases with decreasing  $V_{\text{DD}}$

· degradation of output level

- feedback  $\rightarrow$  node X close to V<sub>DD</sub>

- V<sub>DS</sub> of middle transistor close to zero

- V<sub>GS</sub> of middle transistor below zero

- $\rightarrow$  leakage quenching

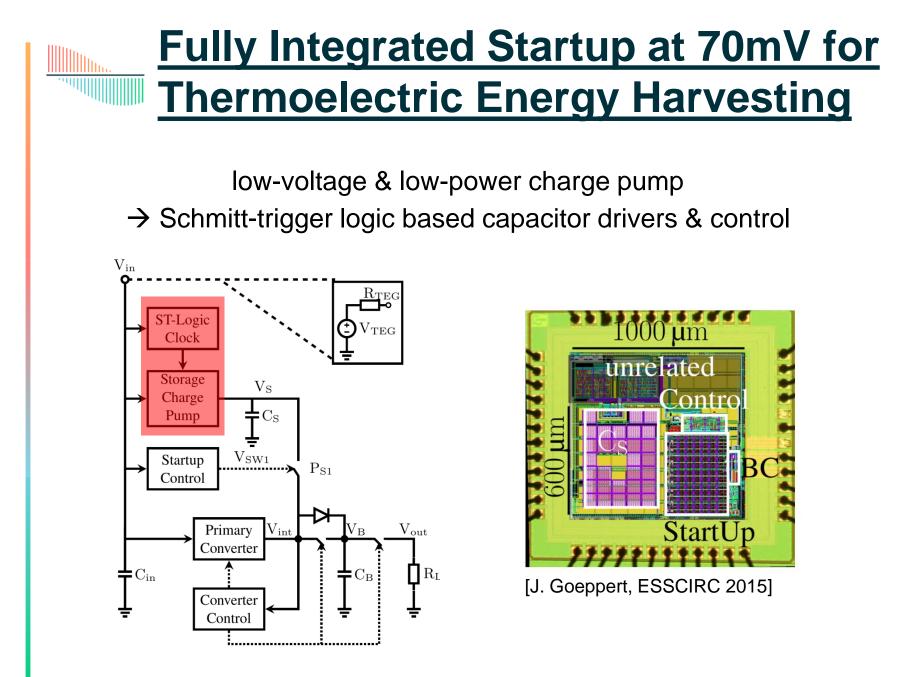

#### **Our Schmitt-trigger Based Digital Standard Cell Library** File Edit View Design Manager Help cādence Show Categories Show Files ell Library View stPara schematic inv DFF Size E- CadenceLibs View Lock ULVLIBS layout 48k nand LULVS1 nor symbol 23k ULVS4 📖 ULVS16 🗄 💥 XFABLibs 🛄 ffPara 📖 sstPara 📖 stParaB S Lib: stPara Free: 218.25G Q D٠ & **b**— Z Α **b**— Z ≥1 B B **D**-flipflop 2-input 2-input inverter NAND NOR with set / reset

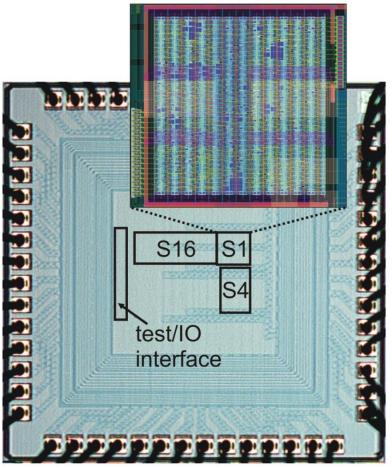

## Our Benchmark Circuit – 8b x 8b Multiplier

- silicon area

- S1: 141µm x 136µm = 19176µm<sup>2</sup>

- S4:  $127\mu m \times 189\mu m = 24003\mu m^2$

- S16:  $343\mu m \times 132\mu m = 45276\mu m^2$

- fully-automated standard-cell design

- measured minimum supply voltage: 84mV (S1), 68mV (S4), 62mv (S16)

- frequency: a few kHz @ 62mV

[N. Lotze, ISSCC 2011]

- µTEG Design & Implementation

- Integrated Digital Circuit Design

@ Ultra-low Supply Voltages

- Conclusion

Performing thermal energy harvesting poses challenges on the

design & implementation of

- thermoelectric generators

- integrated circuits

# Meeting these challenges may pave the way for new integrated energy-autonomous thermal devices!

# Thank you for

# your attention!

The research leading to these results was performed in part within the project STREAMS (<u>www.project-streams.eu</u>) and funded by the European Community's program Horizon 2020 under Grant Agreement 688564.